What is Physical Design Rule Checking (Physical DRC)?

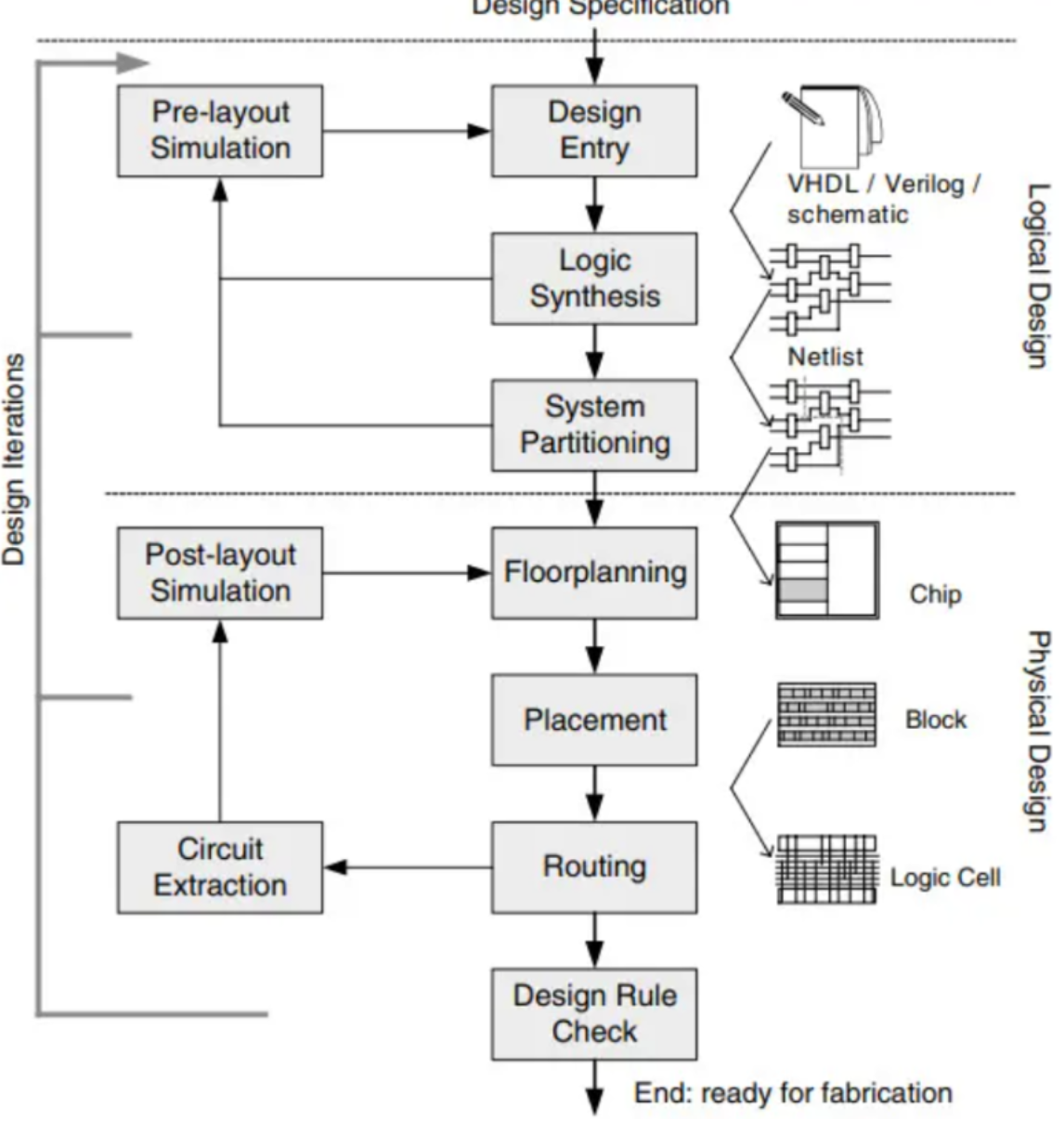

Physical Design Rule Checking (DRC) is the cornerstone of semiconductor physical verification, ensuring that an integrated circuit’s layout adheres to the foundry’s manufacturing constraints. By automating the validation of geometric and spacing requirements in chip layouts, DRC prevents catastrophic defects—shorts, opens, misalignments—and secures high yields, manufacturability, and reliability.

1. Role of DRC in Physical Verification

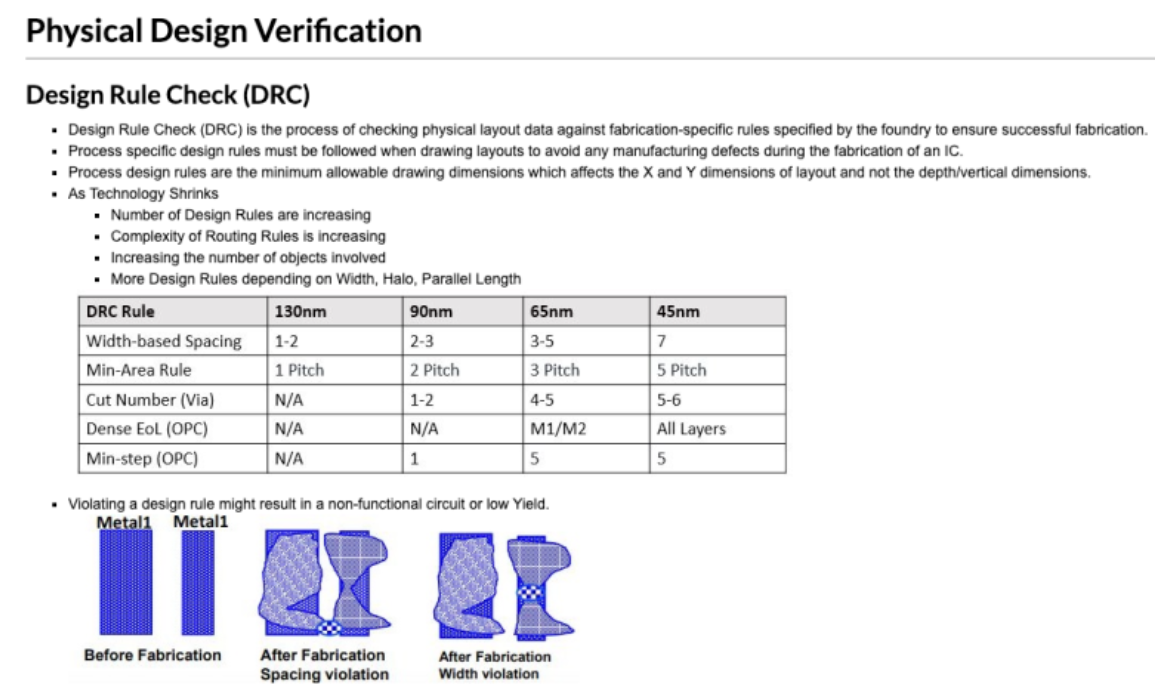

After placement and routing, every layout must satisfy a vast set of design rules supplied by the foundry’s Process Design Kit (PDK). These rules encode minimum widths, spacing, overlap, area, and notch constraints that account for lithography and etch process variations. As a final gatekeeper before tape-out, DRC flags violations that, if left unresolved, could translate into fabrication failures or degraded circuit performance.

2. Key Categories of Design Rules

- Minimum Width: Ensures wires and polysilicon features retain sufficient width to survive etch and carry current without breaking.

- Minimum Spacing: Prevents adjacent shapes from shorting or creating excessive parasitic coupling, including specialized End-of-Line (EOL) spacing at feature ends.

- Enclosure (Overlap): Requires vias, wells, and bond pads to be properly surrounded by metal or implant layers, safeguarding vertical connectivity and reliability.

- Minimum Area: Mandates a minimum polygonal area to avoid feature disappearance during fabrication; also applies to holes within large shapes.

- Notch Rules: Limits re-entrant or “U-shaped” indentations to avoid unpredictable fill or voids.

- Specialized Rules: Wide-metal constraints, jog limits, density and stacking restrictions, different-net spacing, double-patterning assignments, and antenna rules further refine layout integrity.

3. PDK and Rule-Deck Management

PDKs bundle cell libraries, SPICE models, and extensive rule decks. Each rule deck—often numbering in the hundreds or thousands—derives from foundry process engineers.

4. Industry-Standard DRC Engines

Siemens Calibre

- Architecture: Calibre nmDRC leverages multi-threading and distributed computing across on-premise or cloud clusters (GridRun™) to process large designs.

- Rule Scripting: Calibre RULESCRIPT (TCL-based) allows granular, process-specific customizations and edge-case extensions.

- Interactive Debug: Calibre Interactive’s Rule Context Viewer enables dynamic rule-parameter tweaking, while YieldEnhancer predicts each violation’s impact on shorts, opens, and misalignments.

Synopsys IC Validator (ICV)

- In-Memory Engine: A C++ core with optional GPU acceleration delivers ultra-fast, in-memory DRC.

- Live-Debug GUI: Real-time color-coded violation highlighting and drill-down navigation by layer, net, or severity.

- Scripting & APIs: A Python API enables custom validation scripts, batch reporting, and integration with Synopsys TAS for regression testing.

- Incremental DRC: In-Design Incremental DRC rechecks only modified regions after ECO, reducing runtime by over 70%.

5. Advanced Debugging and ECO Strategies

- Violation Analysis: Identify rule types and visualize hotspots through GUI debuggers.

- ECO Execution: Widen wires, adjust spacing, modify enclosure margins, or insert dummy metals.

- Automation: Employ Fusion Compiler or IC Compiler for automated DRC-fix routines, supplemented by custom Python/TCL scripts for recurring patterns.

- Performance Profiling: Analyze CPU and memory logs, then distribute rule groups or layers to optimize throughput.

This is a nice reference:

![[STA] Synchronous Clocks vs. Asynchronous Clocks](https://images.unsplash.com/photo-1533749047139-189de3cf06d3?crop=entropy&cs=tinysrgb&fit=max&fm=jpg&ixid=M3wxMTc3M3wwfDF8c2VhcmNofDF8fGNsb2NrfGVufDB8fHx8MTc1NTQzMzg1OHww&ixlib=rb-4.1.0&q=80&w=600)